0x222 Memory

This paper is a good summary about memory hardware aspects

1. Basic

Memory are not only SRAM and DRAM, traditionally, we have the following technologies for the memory purpose. Watch this video from Crash Course.

- delay line memory (1944): store bit as sound pulse inside a long tube, which be can be detected with a microphone and then cycle back using transducer (speaker). This was used in EDVAC and EDSAC

- core memory (1951): induce a magnetic field into a tiny magnetic ring (core).

1.1. Cache

Cache is usually implemented with SRAM

1.1.1. Hierarchy

- L1: reference 1ns, usually in core

- L2: reference 4ns, usually out core

- L3: usually shared by multiple cores

1.1.2. Placement Policy

- full associative cache: each memory can be placed anywhere

- directed mapped cache: each memory can be placed at one place

- LRU: Least Recently Used

1.1.3. Management

- Write-through: write data to cache and RAM at the same time

- Write-back: delay writing data to RAM

1.2. Memory Controller

1.2.1. MMU

the unit to translate virtual address into physical address

1.2.2. TLB

- the cache that saves the recent address mapping

- it is a cache of page tables

- only store the final translation even it is a multiple-level memory

- change cr3 in x86 can clear TLB automatically

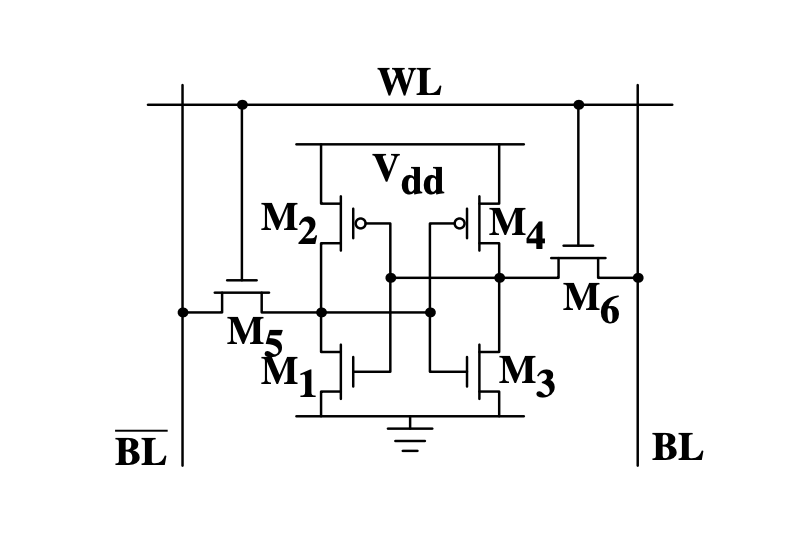

SRAM

Static RAM is implemented with 6 transistors:

- 2 inventors (each has 2 transistor): M1 - M4

- 2 transitor connected to wordline: M5 - M6

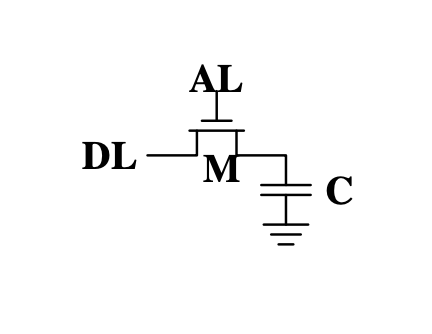

DRAM

Dynamic RAM is implmented with 1 transitor and 1 capacitor

Reading the cell discharges the capacitor, so it has to be recharged. And since capacity of each capacitor has to be kept low, it takes a short time for electrons to dissipate (called leakage). DRAM cell has to be constantly refreshed (e.g. 64ms)